ScuzzBlog: Diaries August 2019

Entry 24th August 2019: Post 01: Acorn "At the RISC of repeating myself".

Acorn "At the RISC of repeating myself"

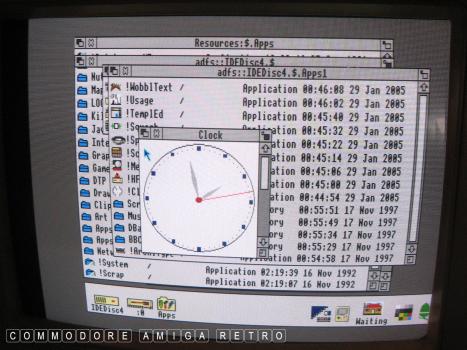

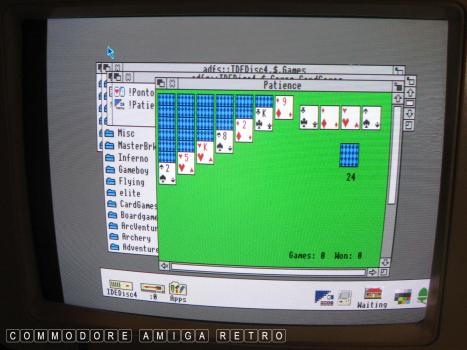

I am at that stage with the diary entries that I am likely to be

repeating myself as I tend to go in a cycle of working with the

collection. I could simply keep repeating the photographic process

but I doubt that is going to be worthwhile. So at times I will be

absent from the blogs, but trust me I am deep in retro territory

but just not photographing the process. And so as I spend some

time this week mucking around with Acorns I will not bore you

with the photographs.

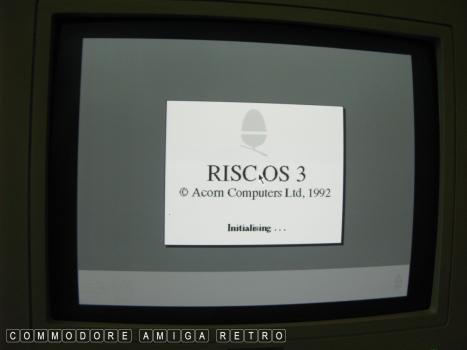

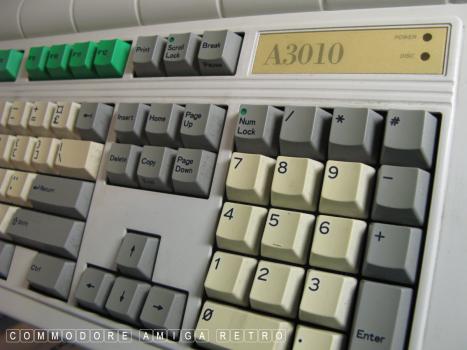

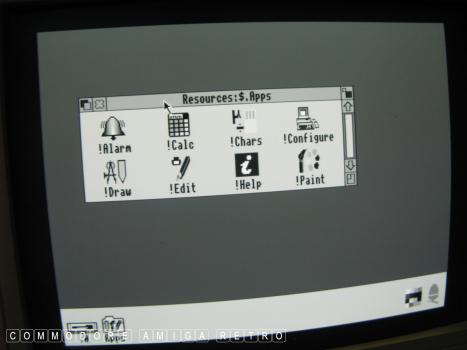

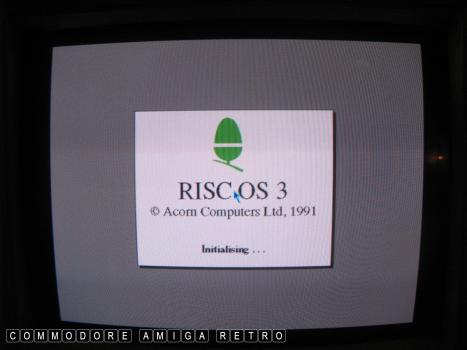

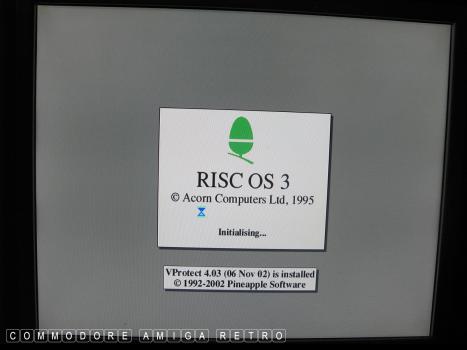

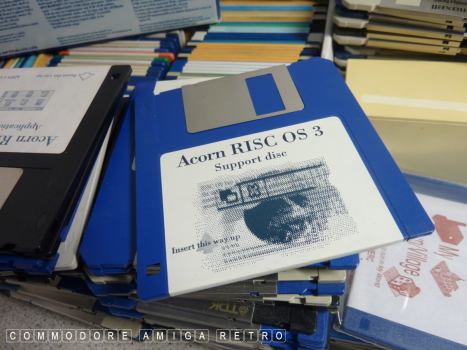

I did fail yesterday to explain the RISC system of computers

and so provide the following. I also feature some quite random

pictures from the collection.

R I S C

Reduced Instruction Set Computer and reduced set against say the

Motorola 68000 on the basis that only 20% of instructions are

generally used. RISC identifies simple instructions and deals with

them and takes complex instructions and converts them into a series

of simple instructions. A complex instruction machine of the day

always ran 'all' instructions as complex and so wasted a lot more

time than the RISC based machines. Whilst the complex instruction

machines used software support to execute the instruction sequence,

all processes on the RISC processor are actually encoded into the chip.

RISC was actually an IBM idea and the first RISC based single chip

microprocessor was built at the University of California. Acorn

themselves started work on the RISC chip in 1983. It took two years

to develop the ARM chips.

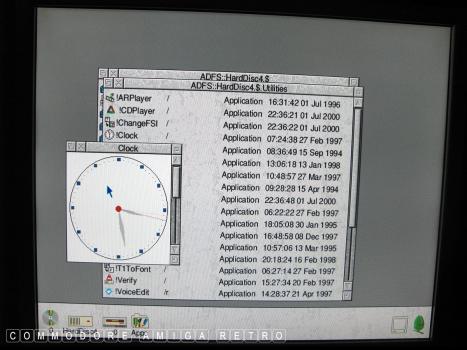

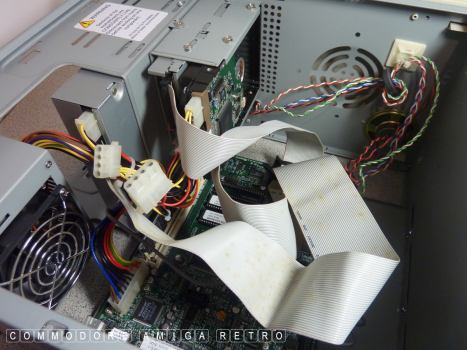

The Acorn Archimedes board uses a 4 layer board and requires a

special extraction tool to de-solder the board. The unit uses a full

32 bit processor and therefore there are 32 signals coming out of

the ARM chip which require 32 tracks for the data bus. The unit

also has a 26 bit address bus and the computer can deal with 64 bytes

of memory. And so the complex data system called for the 4 layer board.

The board has four large main chip sets... The CPU [ ARM ] chip,

memory controller [ MEMC ], input ouput controller [ IOC ] and

video controller [ VIDC ]. Additionally there are four ROM chips.

The backplane supports podules. The backplane is a form of daughter-

board. The 310 has a full 1 MB memory.

The fan housing is fitted only when the podules are included with the

machine.

And ARM stands for ACORN RISC MACHINE and inside the RISC chip [ Reduced

Instruction Set Computer ] which control the ROM and instructions

from the machine.

Watch the whole Acorn video by clicking this link.

*Not sure if the guy actually meant 26 bit address bus. Maybe 32 bit

Acorn "At the RISC of repeating myself"

|

![]()

![]()